Avec les progrès continus de la technologie des semi-conducteurs, le carbure de silicium (SiC), en tant que matériau haute performance, a montré un grand potentiel d'application dans le domaine des appareils électroniques de puissance. Cependant, dans le processus de préparation du substrat en carbure de silicium, le contrôle de la qualité de la surface est particulièrement critique, en particulier après l'amincissement, le meulage et le polissage et d'autres processus visant à obtenir une surface ultra-lisse. Parmi eux, le polissage chimico-mécanique (CMP), en tant qu'une des étapes clés, revêt une grande importance pour éliminer la couche endommagée laissée par le processus précédent et obtenir un nivellement élevé de la surface. Cependant, le procédé CMP traditionnel est confronté au problème du faible taux d'enlèvement de matière (MRR), qui affecte directement l'efficacité et le coût de la production. Par conséquent, l’exploration de nouvelles technologies pour améliorer l’efficacité CMP du substrat SiC est devenue le centre de la recherche actuelle.

1. Principes de base et défis du substrat SiC CMP

La profondeur des dommages de surface du substrat SiC aminci ou broyé est généralement de 2 à 5 μm et nécessite un traitement supplémentaire par CMP.

La technologie CMP est basée sur le principe composite « chimique + mécanique », grâce à la combinaison de la formation d'une couche d'oxyde et de l'élimination mécanique, pour obtenir un lissage de surface.

2. Un faible MRR est le principal problème du CMP du substrat SiC, et l'efficacité CMP du SiC est nettement inférieure à celle du substrat de silicium.

L'impact d'un faible MRR sur l'efficacité et les coûts de production :

Un MRR plus faible entraîne des étapes CMP du substrat SiC plus longues, ce qui augmente le temps et les coûts de traitement.

Même si la méthode CMP existante peut produire un substrat 4H-SiC qualifié, sa faible efficacité reste le goulot d'étranglement limitant son application à grande échelle.

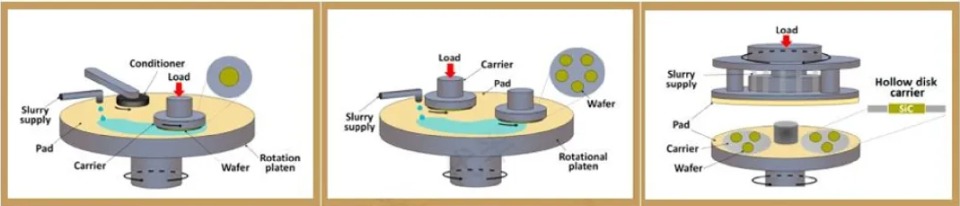

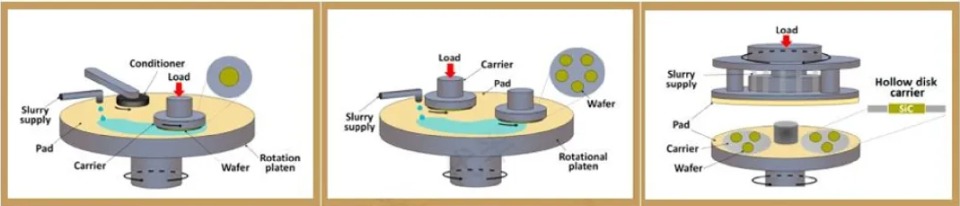

Processus de polissage CMP

3. Des progrès techniques pour améliorer l’efficacité du CMP :

Pour relever le défi du faible MRR, l'industrie a développé une technologie de polissage par lots double face.

Ces technologies avancées ont considérablement réduit les heures de travail CMP, comme le temps de polissage CMP pour un seul lot de 10 substrats de 3 à 5 heures à 1 heure.

La technologie de polissage double face améliore non seulement l'efficacité, mais aide également à maintenir la cohérence et la planéité des deux côtés du substrat.

En résumé, l'amélioration de l'efficacité du polissage chimico-mécanique du substrat en carbure de silicium est la clé pour promouvoir sa large application. Grâce au développement de technologies avancées telles que le polissage double face et par lots, le problème du faible taux d'enlèvement de matière dans le processus CMP traditionnel est efficacement résolu, le temps de traitement est considérablement raccourci et le coût de production est réduit. À l'avenir, avec l'amélioration continue des exigences de performance des matériaux SiC et l'innovation continue de la technologie de polissage, nous avons des raisons de croire que la préparation des substrats SiC sera plus efficace et économique, jetant ainsi une base solide pour le développement ultérieur de appareils électroniques de puissance. Par conséquent, l’exploration et l’optimisation continues du processus CMP constitueront un moyen important de promouvoir une large application des matériaux SiC dans le domaine des semi-conducteurs.